Name des Teilnehmers: Peter Munk

Beschreibung des IT-Forschungsprojekts: In der Vergangenheit zeigte sich, dass der Energieverbrauch mit steigender Komplexität und Taktfrequenz eines einzelnen Prozessorkerns ab einem gewissen Grad aus technologischer und ökologischer Sicht nicht mehr zweckmäßig ist. Die Anzahl der Transistoren pro Chip steigt aber weiterhin entsprechend dem Mooreschen Gesetz, folglich finden alle 12-24 Monate doppelt so viele integrierte Schaltkreise auf der gleichen Chipfläche Platz. Deshalb ist die Halbleiterindustrie dazu übergegangen, die Anzahl der Prozessorkerne pro Chip zu erhöhen. Im Jahr 2014 wurde der erste Many-Core Prozessor mit über Tausend unabhängigen Prozessorkernen vorgestellt.

Aufgrund des steigenden Rechenbedarfs zukünftiger eingebetteter Anwendungen, wie z.B. dem hochautomatisierte Fahren, werden Many-Core Prozessoren auch für den Einsatz in eingebetteten Systemen zunehmend interessanter. Diese eingebetteten Systeme finden ihre Anwendung häufig im Kontext von harten Echtzeitanforderungen und innerhalb sicherheitskritischer Systeme.

Die Rechenleistung von Many-Core Prozessoren basiert auf der hohen Anzahl von Transistoren pro Chip, welche wiederum auf eine schrumpfende Strukturbreite zurückgeht. Dies hat ebenfalls zur Folge, dass die Anfälligkeit der Hardware für transiente Fehler steigt. Transiente Fehler entstehen durch Einschläge von geladenen Teilchen auf dem Chip und resultieren zum Beispiel zu bit flips, also in Veränderungen von Werten in Speicherzellen.

Sicherheitsmechanismen zum Schutz vor diesen transienten Fehlern wurden bislang häufig in Hardware umgesetzt. Dies erhöht allerdings die Stückkosten, da zumeist zusätzliche Chipfläche oder sogar zusätzliche Chips benötigt werden. Außerdem sind Hardwaremaßnahmen häufig nicht in kostengünstigen consumer electronic Prozessoren zu finden, welche in großen Stückzahlen produziert werden. Gerade diese consumer electronic Prozessoren sind für Industrien mit hohen Stückzahlen wie der Automobilbranche aber besonders attraktiv.

Die inhärente räumliche Redundanz, sprich die große Anzahl an Rechenkernen in Many-Core Prozessoren ermöglicht es, die bisher in Hardware umgesetzten Methoden, wie z.B. N-Modular-Redundancy (NMR), prinzipiell in Software abzubilden. So kann die gleiche Anwendung auf N Kernen parallel ablaufen und die Ergebnisse der einzelnen Ausführungen können anschließend auf einem weiteren Rechenkern verglichen werden. Ein solcher Vergleich kann die Sicherheit eines Systems erhöhen, da festgestellt werden kann ob transiente Fehler auf einem Kern aufgetreten sind. Für den Fall, dass mehr als zwei Ausführungen verglichen werden, kann ein solcher Fehler nicht nur erkannt sondern auch behoben werden.

Innerhalb des Mikroprojekts wurden Software-implementierte Sicherheitsmechanismen für sicherheitskritische Echtzeitanwendungen auf Many-Core Prozessoren erforscht und prototypisch implementiert. Zur Erhöhung der Fehlertoleranz wurde ein auf NMR basierender Ansatz entwickelt und kontinuierlich verbessert.

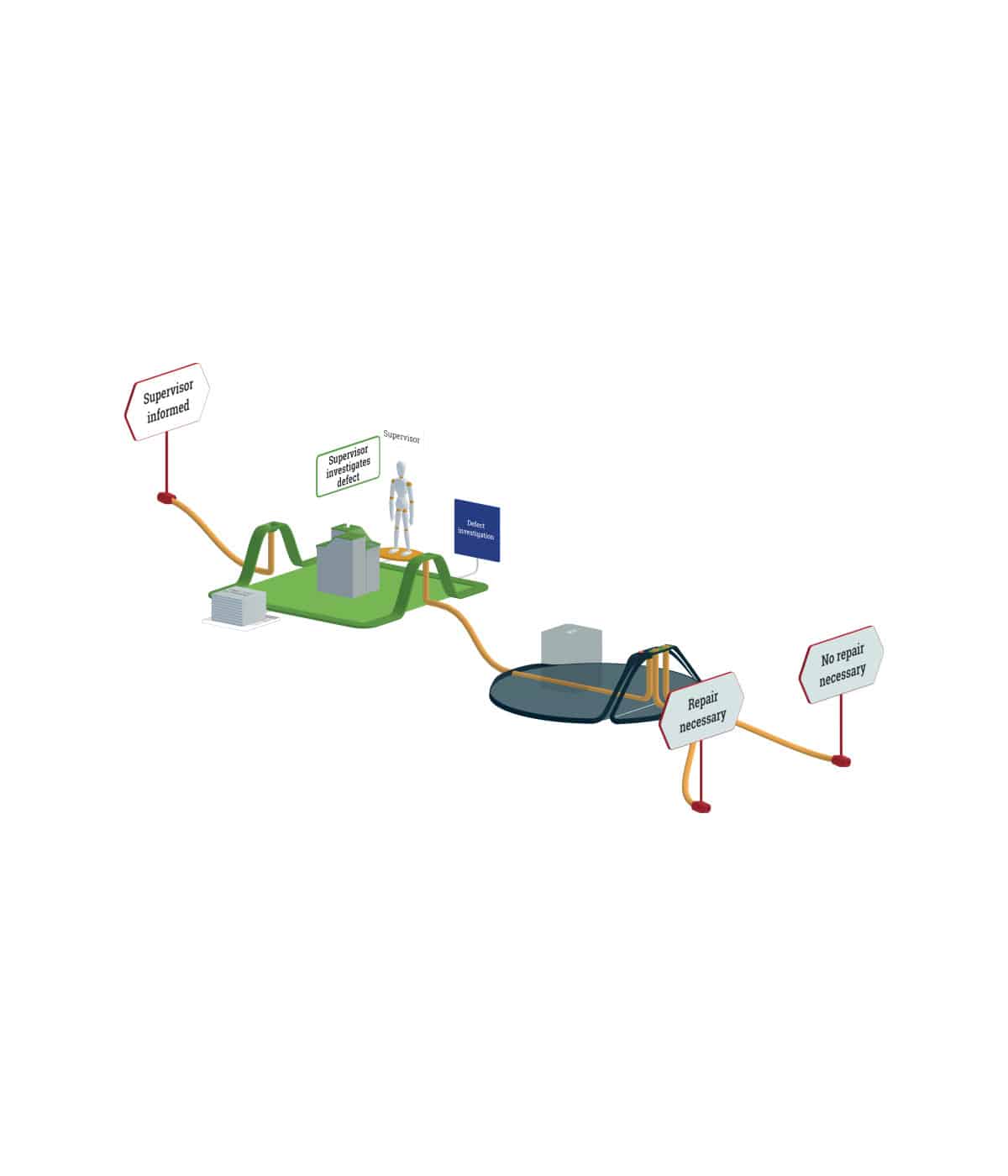

Zudem wurde ein Verfahren zur Absicherung der NMR Vergleichseinheit erstellt. Die zugrundeliegende Idee ist dabei, zwei fail-silent Vergleichseinheiten einzusetzen, die sich gegenseitig kontrollieren. Fail-silent bedeutet, dass jede Vergleichseinheit einen internen Fehler selbst erkennt und sich abschaltet. Die Erkennung interner Fehler ermöglicht eine ANBD-Kodierung der Vergleichsroutine. Dabei wird während dem Vergleich eine Prüfsumme errechnet, welche anschließend mit einem statischen Wert vergleich wird, um so Fehler im Ablauf des Vergleichsalgorithmus zu erkennen.

Neben einer Fehlererkennungsfunktion wurde ein Reparaturmechanismus entwickelt, welcher die Fehlertoleranz des Gesamtsystems zusätzlich anhebt. Dieser Reparaturmechanismus basiert auf dem Einsatz von zusätzlichen Softwarekomponenten auf unabhängigen Kernen, sogenannten Spares, die im Fehlerfall die Berechnung von einer fehlerhaften Softwarekomponente übernehmend, während diese repariert wird.

Die durch den Sicherheitsmechanismus hinzugewonnene Funktionalität wird dem Anwender in komfortabler Weise als Framework zur Verfügung gestellt. Der Anwender spezifiziert dabei die gewünschte Zuverlässigkeit und Verfügbarkeit einer Softwareeinheit und das Framework passt den entwickelten Sicherheitsmechanismen so an, dass diese Werte mit minimaler zusätzlicher Systemlast erreicht werden. Die Zuverlässigkeit und Verfügbarkeit des Systems wird durch ein mathematisches Modell des Sicherheitsmechanismus basierend auf einer zeitdiskreten Markow-Kette berechnet.

Sowohl die Korrektheit des mathematischen Modells als auch die zusätzliche Systemlast wurden durch eine Implementierung des Sicherheitsmechanismus auf einem Zyklen-akkurat simulierten Many-Core Prozessor gezeigt.

Das innerhalb des Mikroprojekts prototypisch entwickelte Framework kann die Entwicklung sicherheitskritischer Echtzeitsoftware auf Many-Core Prozessoren erleichtern. Der enthaltene Software-implementierte Sicherheitsmechanismus ist für alle Industriebereiche mit Echtzeitanwendungen interessant, da er es ermöglicht, die Hardwarekosten unter Einhaltung der funktionalen Sicherheitsanforderungen zu verringern.

Software Campus-Partner: TU Berlin, Robert Bosch GmbH

Umsetzungszeitraum: 01.03.2014 – 31.10.2015